FUNCTIONAL SPECIFICATIONS OF THE ANNULAR SUSPENSION POINTING SYSTEM

bу

Bryan Edwards Department of Computer Science University of Colorado at Boulder Boulder, Colorado

CU-CS-171-80

January, 1980

This work was supported by grant NSG 1638 from NASA Langley Research Center.

# Abstract

The following is a description of the Annular Suspension Pointing System. This description is written using the Design Realization, Evaluation and Modelling (DREAM) system, and its design description technique, the DREAM Design Notation (DDN).

Appendix A contains a DDN description of the Annular Suspension Pointing System. The information contained in this description was derived from the NASA-produced report, "The Executive Software For the Annular Suspension Pointing System," which appears as Appendix B. The description is divided into four major sections.

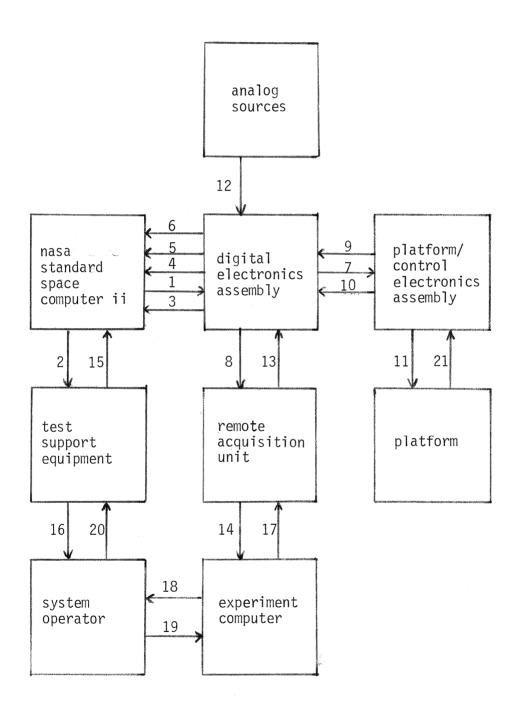

The first section of Appendix A (System Overview) contains the major units of the system, their interconnections, and the event flow between these units. Figure 1 corresponds to Figure 1 in the original report, with the addition of three major units: analog sources, experiment computer, and the system operator. Additional communication paths are also shown. Each communications path is labeled with a number. These numbers correspond to the CONNECTIONS given in the DREAM description. In addition, the EVENT DEFINITIONS reference the communications paths which the events use, by appending the path number to the event name. Finally, the legal event sequences are given in the DESIRED BEHAVIOR section of the description, using a regular expression type notation. In this section, a shorthand, non-standard, notation is used to indicate the repetition of a sequence of events a specific number of times.

The second section (LEVEL II) describes the basic operations of each of the major units of the system. The input and output ports are identified, and an abstract model of the operation is given in terms of the input and output.

In the third section (LEVEL III), the notion of the internal servicers P(1), P(2) and P(3) is introduced. The internal operation of these servicers is not detailed. The logical interaction between the servicers and the input and output ports of the NASA standard space computer is given.

The notion of the time intervals T(1), T(2) and T(3) is introduced in the fourth section (LEVEL IV). Here we see the interaction between the master timing pulse and the signals to the three processes P(1), P(2) and P(3).

In Appendix B, we have included a copy of the NASA-produced functional specification of the Annular Suspension Pointing System.

The portions of the report which were captured by the DDN description of the system are underlined.

Some portions of the NASA report contain very detailed descriptions of sections of the system. This detail is not reflected in the DDN description. Further elaborations of the DDN description would be required to capture this detail.

The DDN description does not capture the notion of the mode (idle, coarse, fine, slew) of the system, and the details of the data communicated between the system units is not given. The NASA report does not contain enough information in these areas to allow further elaboration.

In preparing the DDN description, the concepts available in DDN were adequate to describe most of this embedded computer system. The only area that DDN does not adequately describe is the notion of a specific interval of time.

# Appendix A:

DREAM Design Notation Description of Annular Suspension Pointing System

```

SYSTEM OVERVIEW

[annular suspension pointing system]:

SUBSYSTEM CLASS;

DOCUMENTATION:

The purpose of the ASPS is to control a platform which will be

flown on the space shuttle. Equipment (e.g., a telescope) will be mounted on the platform and the ASPS will allow this equipment to be pointed in a given direction with extreme accuracy (\pm 4.84 \times 10^{-7}

radians) and this position maintained for extended periods (stability

\pm 4.84 \times 10^{-8} radians /sec) in the presence of shuttle disturbances.

END DOCUMENTATION:

QUALIFIERS:

t1 per t2, t2 per t3

END QUALIFIERS;

SUBCOMPONENTS:

nsscii

OF [nasa standard space computer ii],

dea

OF [digital electronics assembly],

OF [test support equipment],

tse

rau

OF [remote acquisition unit].

OF [experiment computer],

ec

pea cea OF [platform electronics assembly control electronics

assemblv1.

OF [platform].

р

OF [analog sources],

as

OF [system operator]

SO

END SUBCOMPONENTS:

CONNECTIONS:

PLUG (nsscii | dea outputs, dea | nsscii inputs),

1

PLUG (nsscii | tse outputs, tse | nscii inputs),

2

PLUG (dea | nsscii outputs, nsscii | dea inputs),

3

PLUG (dea t1 tick

, nsscii tl tick),

4

```

, nsscii t2 tick),

5

PLUG (dea|t2 tick

```

PLUG (dea | t3 tick

, nsscii|t3 tick),

6

PLUG (dea pea cea outputs, pea cea dea inputs),

7

PLUG (dea | rau outputs

, rau dea inputs),

8

PLUG (pea cea master timing pulse, dea master timing pulse),

9

PLUG (pea cea dea outputs, dea pea cea inputs),

10

PLUG (pea cea | p outputs, p | pea cea inputs),

11

PLUG (as dea outputs, dea as inputs),

12

PLUG (rau|dea outputs, dea|rau inputs),

13

PLUG (rau ec outputs, ec rau inputs),

14

PLUG (tse|nsscii outputs, nsscii|tse inputs),

15

PLUG (tse so outputs, so tse inputs),

16

PLUG (ec|rau outputs, rau|ec inputs),

17

PLUG (ec|so outputs, so|ec inputs),

18

PLUG (so ec outputs, ec so inputs),

19

PLUG (so tse outputs, tse so inputs),

20

PLUG (p|pea cea outputs, pea cea|p inputs),

21

END CONNECTIONS:

```

```

[asps_operation]: EVENT CLASS;

```

EVENT DEFINITION;

system operator request experiment 19: DESCRIPTION;

This event corresponds to the system operator entering a request, at the operator console, to the experiment computer.

END DESCRIPTION;

experiment computer request platform action 17,13: DESCRIPTION;

In order to perform a given experiment, the experiment computer must manipulate the platform in some predefined manner.

END DESCRIPTION;

dea request computation 3: DESCRIPTION;

Many times, computations must be performed before a requested platform action can occur.

END DESCRIPTION;

nsscii computation result returned 1: DESCRIPTION;

Computations supporting the platform are performed in the nsscii. Results are returned to the dea.

END DESCRIPTION:

dea request platform action 7,11: DESCRIPTION;

The platform is actually controlled by the pea/cea.

END DESCRIPTION;

platform\_responds\_21,10: DESCRIPTION;

The platform responds to request from the pea/cea.

END DESCRIPTION;

platform\_result\_returned\_to\_experiment\_computer\_8,14: DESCRIPTION;

The results of a high-level platform operation are returned to the experiment computer.

END DESCRIPTION;

experiment result returned to system operator 18: DESCRIPTION;

The result of our experiment is returned to the system operator, at the operator console.

END DESCRIPTION;

system operator request test 20: DESCRIPTION;

This event corresponds to the system operator entering a request at the test console, to the test support equipment.

END DESCRIPTION;

tse request action 15: DESCRIPTION;

In order to perform a given test, the test support equipment must get certain data from the nsscii.

END DESCRIPTION:

nsscii result returned 2: DESCRIPTION;

Test data from the nsscii is returned to the test support equipment.

END DESCRIPTION;

test\_result\_returned\_to\_system\_operator\_16: DESCRIPTION;

The result of a test is returned to the system operator, at the test console.

END DESCRIPTION;

master\_timing\_pulse\_9: DESCRIPTION;

This pulse is generated every T(1) milliseconds.

END DESCRIPTION;

t1 timing pulse 4: DESCRIPTION;

This pulse is generated every T(1) milliseconds as a result of the master timing pulse.

END DESCRIPTION;

t2\_timing\_pulse\_5: DESCRIPTION;

This pulse is generated every T(2) milliseconds as a result of the master timing pulse. Note that T(2) milliseconds is an integral multiple of T(1).

END DESCRIPTION;

t3\_timing\_pulse\_6: DESCRIPTION;

This pulse is generated every T(3) milliseconds as a result of the master timing pulse. Note that T(3) milliseconds is an integral multiple of T(2).

END DESCRIPTION;

```

DESIRED BEHAVIOR:

SHUFFLE(

REPEAT(

SEQUENCE(

SEQUENCE(

SEQUENCE(master_timing_pulse_9, t1_timing pulse 4), ^{t1_per_t2}

t2_timing_pulse 5), t2_per_t3

t3 timing pulse 6)),

REPEAT (

SEQUENCE(

system operator request experiment 19,

REPEAT(

SEOUENCE(

experiment computer requests platform action 17,13,

REPEAT

(SEOUENCE

(dea request computation 3,

nsscii computation result returned 1)),

REPEAT

(SEQUENCE

(dea request platform action 7,11,

platform responds 21,10)),

platform result returned to experiment computer 8,14)).

experiment result returned to system operator 18)),

REPEAT(

SEQUENCE(

system operator request test 20,

REPEAT(

SEQUENCE(

tse request action 15,

nsscii results returned 2)),

test result returned to system operator 16)))

END DESIRED BEHAVIOR:

END EVENT DEFINITION;

END EVENT CLASS;

END SUBSYSTEM CLASS;

```

```

[system operator]: SUBSYSTEM CLASS;

ec outputs: OUT PORT;

END PORT;

tse outputs: OUT PORT;

END PORT;

ec inputs: IN PORT;

END PORT;

tse inputs: IN PORT;

END PORT:

operator: CONTROL PROCESS;

MODEL;

ITERATE

SELECT

(PERHAPS): SEND

ec outputs;

(PERHAPS): SEND tse outputs;

END SELECT;

SELECT

(PERHAPS): RECEIVE ec inputs;

(PERHAPS): RECEIVE tse_inputs;

END SELECT;

END ITERATE;

END MODEL:

END CONTROL PROCESS;

END SUBSYSTEM CLASS;

```

```

[experiment computer]:

SUBSYSTEM CLASS;

rau outputs:

OUT PORT;

END PORT;

so_outputs:

OUT PORT;

END PORT;

rau_inputs:

IN PORT;

END PORT;

so_inputs:

IN PORT;

END PORT;

experiment:

CONTROL PROCESS;

MODEL;

ITERATE

RECEIVE so inputs;

SEND

rau outputs:

RECEIVE rau-inputs;

SEND

so outputs;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

END SUBSYSTEM CLASS;

```

```

LEVEL II

[remote acquisition unit]: SUBSYSTEM CLASS;

dea outputs: OUT PORT;

END PORT;

ec outputs: OUT PORT;

END PORT;

dea inputs: IN PORT;

END PORT;

ec inputs: IN PORT;

END PORT;

acquisition: CONTROL PROCESS;

MODEL;

ITERATE

RECEIVE ec inputs;

SEND

dea outputs;

RECEIVE dea inputs;

SEND

ec outputs;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

```

```

[platform]: SUBSYSTEM CLASS;

```

pea\_cea\_outputs: OUT PORT; END PORT;

pea\_cea\_inputs: IN PORT; END PORT;

platform: CONTROL PROCESS;

MODEL;

ITERATE

RECEIVE pea\_cea\_inputs; SEND pea cea outputs;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

[analog\_sources]: SUBSYSTEM CLASS;

dea\_outputs: OUT PORT;

END PORT;

source: CONTROL PROCESS;

MODEL;

ITERATE

SEND dea\_outputs;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

```

[test support equipment]: SUBSYSTEM CLASS;

nsscii outputs: OUT PORT;

END PORT;

so outputs: OUT PORT;

END PORT;

nsscii inputs: IN PORT;

END PORT;

so inputs: IN PORT;

END PORT;

support: CONTROL PROCESS;

MODEL;

ITERATE

RECEIVE so inputs;

SEND

nsscii outputs;

RECEIVE nsscii_inputs;

SEND

so outputs;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

```

```

[platform_electronics_assembly_control_electronics_assembly]: SUBSYSTEM

CLASS;

master timing pulse: OUT PORT;

END PORT;

dea outputs: OUT PORT;

END PORT;

p outputs: OUT PORT;

END PORT;

dea inputs: IN PORT;

END PORT:

p inputs: IN PORT;

END PORT;

control: CONTROL PROCESS;

MODEL;

ITERATE

SELECT

(PERHAPS): SEND master timing pulse;

(PERHAPS): RECEIVE dea inputs;

SEND

p outputs;

RECEIVE p inputs;

SEND

dea outputs;

END SELECT;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

END SUBSYSTEM CLASS;

```

```

[nasa standard space computer ii]: SUBSYSTEM CLASS;

dea outputs:

OUT PORT;

END PORT;

tse outputs: OUT PORT;

END PORT;

dea inputs: IN PORT;

END PORT;

t1 tick: IN PORT;

END PORT:

t2 tick: IN PORT;

END PORT;

t3 tick: IN PORT;

END PORT;

tse inputs: IN PORT;

END PORT;

nsscii executive: CONTROL PROCESS;

MODEL;

perform initialization;

SEND dea outputs:

RECEIVE dea inputs;

ITERATE

SELECT

(PERHAPS): RECEIVE t1 tick;

SEND

dea outputs;

(PERHAPS): RECEIVE t2 Tick;

(PERHAPS): RECEIVE t3 tick;

(PERHAPS): RECEIVE tse inputs;

SEND

tse outputs;

END SELECT;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

END SUBSYSTEM CLASS;

```

```

[digital_electronics_assembly]: SUBSYSTEM CLASS;

```

nsscii\_outputs: OUT PORT; END PORT;

t1\_tick: OUT PORT; END PORT;

t2\_tick: OUT PORT; END PORT;

t3\_tick: OUT PORT; END PORT;

pea\_cea\_outputs: OUT PORT; END PORT;

rau outputs: OUT PORT;

END PORT;

nsscii\_inputs: IN PORT; END PORT;

master\_timing\_pulse: IN PORT; END PORT;

pea\_cea\_inputs: IN PORT; END PORT;

as\_inputs: IN PORT;

END PORT;

rau\_inputs: IN PORT;

END PORT;

```

dea executive: CONTROL PROCESS;

MODEL;

ITERATE

SELECT

(PERHAPS): RECEIVE master timing pulse;

SEND t1 tick;

SELECT

(PERHAPS) SEND t2 tick;

(PERHAPS) SEND t2 tick;

SEND t3 tick;

END SELECT;

(PERHAPS): RECEIVE rau inputs;

MAYBE

SEND nsscii outputs;

RECEIVE nsscii inputs;

END MAYBE;

MAYBE

SEND pea_cea_outputs;

RECIEVE pea cea inputs;

END MAYBE;

(PERHAPS): RECEIVE as inputs;

END SELECT;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

```

```

'[nasa standard space computer ii]: SUBSYSTEM CLASS'

SUBCOMPONENTS;

p1, p2, p3 OF [process]

END SUBCOMPONENTS;

CONNECTIONS;

PLUG (nsscii executive|p1 initiate, p1|initiate),

PLUG (nsscii executive|p2 initiate, p2|initiate),

PLUG (nsscii executive|p3 initiate, p3|initiate),

PLUG (p1|complete, nsscii executive|p1 complete),

PLUG (p2|complete, nsscii executive|p2 complete),

PLUG (p3|complete, nsscii executive|p3 complete)

END CONNECTIONS;

nsscii executive: CONTROL PROCESS;

pl initiate:

LOCAL OUT PORT;

END PORT;

LOCAL OUT PORT;

p2 initiate:

END PORT;

LOCAL OUT PORT;

p3 initiate:

END PORT;

p1 complete:

LOCAL IN PORT:

END PORT;

p2 complete:

LOCAL IN PORT:

END PORT:

p3 complete

LOCAL IN PORT;

END PORT;

```

```

MODEL;

perform initialization;

SEND dea outputs;

RECEIVE dea inputs;

ITERATE

SELECT

(PERHAPS): RECEIVE t1 tick;

SEND

pl initiate;

(PERHAPS): RECEIVE t2 tick;

p2_initiate;

SEND

(PERHAPS): RECEIVE t3 tick;

SEND

p3 initiate;

(PERHAPS): RECEIVE p1 complete;

dea outputs;

SEND

(PERHAPS): RECEIVE p2 complete;

(PERHAPS): RECEIVE p3 complete;

(PERHAPS): RECEIVE tse_inputs;

SEND

tse outputs;

END SELECT;

END ITERATE;

END MODEL;

```

END CONTROL PROCESS;

```

[process]: SUBSYSTEM CLASS;

```

complete: OUT PORT;

END PORT;

initiate: IN PORT;

END PORT;

process: CONTROL PROCESS;

MODEL;

**ITERATE**

RECEIVE initiate; perform\_operations; SEND complete;

END ITERATE;

END MODEL;

END CONTROL PROCESS;

#### LEVEL IV

```

'[digital electronics assembly]: SUBSYSTEM CLASS'

QUALIFIERS;

t1 per t2, t2_per_t3

END QUALIFIERS;

LOCAL SUBCOMPONENT;

t1 pulses OF [0:: t1 per t2],

t2 pulses OF [0:: t2 per t3]

END LOCAL SUBCOMPONENT;

dea executive: CONTROL PROCESS;

MODEL;

SET t1 pulses T0 0;

SET t2 pulses T0 0;

ITERATE

SELECT

(PERHAPS): RECEIVE master timing pulse;

SEND t1 tick;

SET t1 pulses T0 t1 pulses + 1;

IF t1 pulses = t1 per t2 THEN

SET t1 pulses TO 0;

SEND t2 tick;

SET t2 pulses T0 t2 pulses + 1;

IF t2 pulses = t2 per_t3 THEN

SET t2 pulses TO 0;

SEND t3 tick;

END IF;

END IF;

(PERHAPS): RECEIVE rau inputs;

MAYBE

nscii_outputs;

SEND

RECEIVE nsscii inputs;

END MAYBE

MAYBE

SEND

pea cea outputs;

RECEIVE pea cea inputs;

END MAYBE;

(PERHAPS): RECEIVE as inputs;

END SELECT;

END ITERATE;

END MODEL 3

END CONTROL PROCESS;

```

# Appendix B:

Functional Requirements of Annular Suspension Pointing System

> (Produced by NASA Langley Research Center Personnel)

1

THE EXECUTIVE SOFTWARE FOR THE ANNULAR SUSPENSION POINTING SYSTEM

I. INTRODUCTION.

This document attempts to describe the Annular Suspension Pointing System (ASPS) hardware facilities and the structure of the software executive in sufficient detail that it can be used as an example of the requirements for concurrent programing in NASA embedded computer systems. The hardware details are provided for those who are unfamiliar with the general layout of the ASPS. This description is intended to be accurate and every effort will be made to ensure that it correctly reflects the software currently being written for the ASPS engineering model. The engineering model is a ground-based system used for testing. This is the first version of the software which will be used. This description is also intended to be complete in the sense that the functions of the software is defined in sufficient detail (albeit informally) that only minor parametric details are needed before the software can be constructed.

Two consequences of the fact that the software described is for an engineering model are that the software is instrumented and the existence of a human operator is assumed. The instrumentation is for performance evaluation and error analysis. It will not be specified here since it does not affect the ASPS executive function.

The purpose of the ASPS is to control a platform which will be flown on the Space Shuttle. Equipment (e.g. a telescope) will be mounted on the platform and the ASPS will allow this equipment to be pointed in a given direction with extreme accuracy (+ or - 4.84e-7 radians) and this position maintained for extended periods (stability + or - 4.84e-8 radians per sec.) in the presence of Shuttle disturbances.

#### II. HARDWARE CONFIGURATION OF THE SYSTEM

Figure 1 shows the organization of the major hardware units comprising the ASPS

#### Definitions:

- a) TSE: Test Support Equipment. The TSE consists of a terminal and a computer. It will be used to generate various inputs from the operator and display messages to the operator for ground testing of the ASPS.

- b) NSSC II: NASA Standard Space Computer II. The NSSC II is basically an IBM System 360 computer. It will be used to carry out the computations which implement the control laws for the platform.

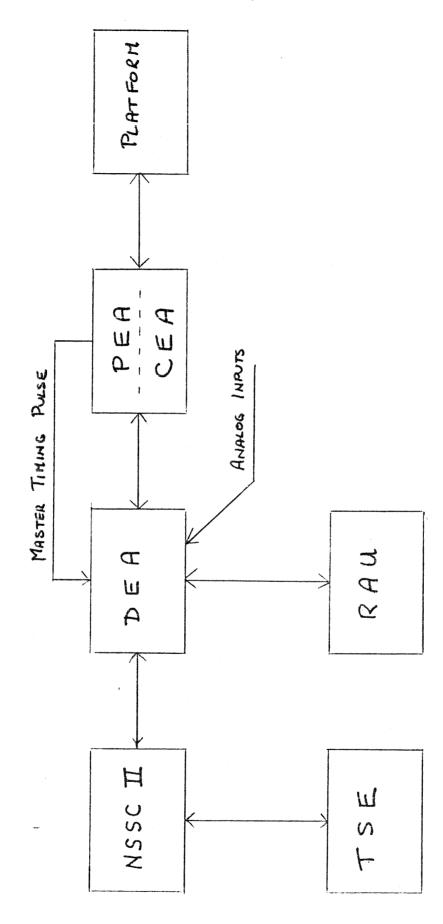

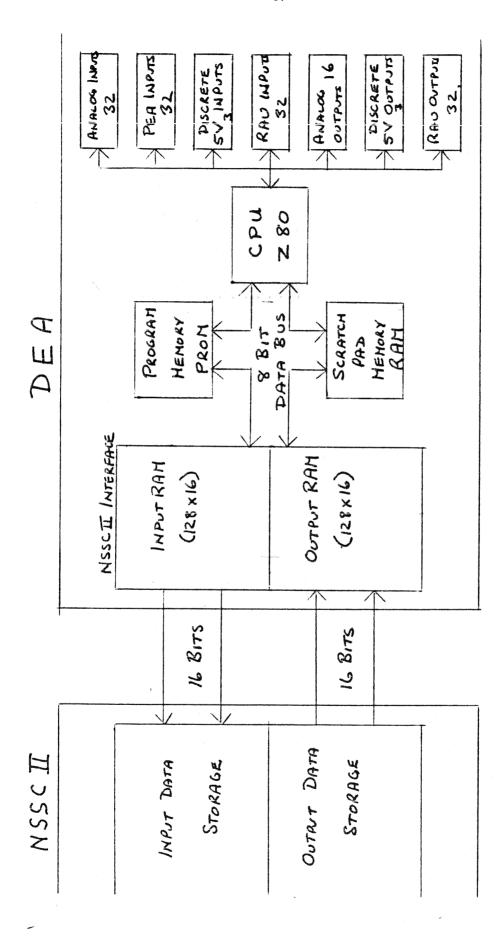

- c) <u>DEA: Digital Electronics Assembly. The DEA is an electronics assembly</u> based on a Z-80 microprocessor which is <u>used as an I/O controller for the NSSC II.</u> Figure 2 shows the major hardware units of the DEA.

- d) PEA/CEA: Platform Electronics Assembly/Control Electronics Assembly. The PEA is the electronic assembly on the platform which, together with the CEA, is responsible for moving the platform and sending position information to the NSSC II.

- e) RAU: Remote Acquisition Unit. The RAU provides 32 digital input and 32 digital output lines. It is connected to the experiment computer i.e. the experiment which is using the ASPS, and all I/O between the DEA and the experiment computer is through the RAU.

The system of interest for the executive consists of an NSSC II computer connected to the DEA. The DEA is connected to the NSSC II by 16 inputs, 16 output and several control lines. During flight all I/O to the NSSC II is through the DEA. In the engineering model, I/O to

the NSSC II can also be from the TSE. Analog data to or from the platform is converted (A/D,D/A) in the DEA and preprocessed in the DEA before being sent to the NSSC II.

The experiment computer sends platform control commands (e.g. point telescope in a particular direction) to the DEA, which in turn requests the NSSC II to compute the control laws. This output is sent through the DEA to the PEA/CEA which moves the platform.

The system master timing pulse is generated by the PEA and sent to the DEA. This is a pulse every T(1) milliseconds which is used for real-time timing. T(1) is a fixed integer whose value has not been finalized.

NOTE: This pulse is <u>not</u> sent directly to the NSSC II.

## III. NSSC II CHARACTERISTICS

This section provides a summary only and is not intended to be complete. Full details of the machine can be obtained from the hardware reference manual.

The NASA Standard Space Computer II (NSSC II) is very much like an IBM System 360. A thorough knowledge of S/360 is assumed in this summary. The NSSC II's instruction set contains 83 of the 87 instructions from the S/360 Standard Set. (Recall that the Standard Set does not include decimal, direct control, protection or floating point instructions.) The exceptions are HIO(9E), SIO(9C), TCH(9F), and TIO(9D). The semantics of these 83 instructions are identical to S/360 except for the following areas:

- (1) The S/360 interval timer at location 80(decimal) is not implemented.

- (2) Effective addresses are limited to 16 bits except for the LA(41) instruction which generates a 24-bit result.

Added to these 83 instructions are three new instructions:

|                    | Mnemonic | Opcode          | Format |

|--------------------|----------|-----------------|--------|

|                    | `        |                 |        |

| Timer Read and Set | TMRS     | A 4             | RS     |

| Start I/O          | SIO      | A5 <sup>†</sup> | RS     |

| Set Storage Key    | SSK      | 08              | RR     |

The NSSC II supports a real-time clock and an interval timer. The real-time clock is 32 bits long, is incremented by I each 112.64 microseconds and causes no interrupt on overflow. The interval timer is 16 bits long, is decremented by I each 112.64 microseconds and generates an external interrupt on change of sign from positive to negative.

The clocks are read, or read and set, individually by the TMRS instruction. Reading yields a timer value in a register. Setting involves a value from storage being placed in the timer.

There are four kinds of I/O. They are:

- (a) Direct.

- (b) Buffered.

- (c) Direct Memory Access (DMA).

- (d) External Interrupt.

Direct I/O constitutes transferring 16 bits of data to/from the NSSC II from/to the DEA via a 16 bit bus. Transfers of this type are the result of the NSSC II executing a SIO instruction. Note that this is totally different from the SIO instruction on S/360.

Buffered I/O is a means of performing block transfers of data to/from the NSSC II memory in parallel with normal execution of the NSSC II. When buffered I/O takes place, memory references and sequencing are controlled by hardware within the CPU but this does not interefere with instruction execution. The NSSC II has provision for up to 16 devices to perform buffered I/O. A fixed storage location is used on the NSSC II to point to a buffered I/O device table with 16 entries. An entry contains two words each of which is a word count and address pair. One word is for input and the other is for output. The word count is number of words to be transferred and the address is the main memory buffer location. If the relevant word count is positive when a buffered  $\ensuremath{\mathrm{I}}/0$  operation begins, then the count is decremented and the address is incremented in the table entry as each word is transferred. When the transfer is complete the word count will be zero (assuming no error). If the word count is initially negative, the word count is modified during the buffered I/O operation but is reset to its original value when the operation completes. The number of words transferred in this case is the absolute value of the word count. A buffered  $\mathrm{I}/\mathrm{O}$ operation is initiated using direct I/O (SIO instruction) to send 16

bits of data to the device which will perform the operation.

Direct memory access is literally direct access of the NSSC II memory. The ASPS system does not use DMA.

An external interrupt changes the state of the NSSC II as a result of an external stimulus and as such can be regarded as an input mechanism. The ASPS system does not use external interrupts for data input.

Memory on the NSSC II is protected in blocks of 1024 bytes. Storage keys are two bits long, and they are used for write protection only. One bit is used to inhibit CPU and buffered I/O storing and the other is used to inhibit DMA storing. Storage keys are set by the Set Storage Key (SSK) instruction, and also, following an interrupt, the storage key of the first block of memory is set to allow CPU and Buffered I/O storing but inhibt DMA storing. No other storage keys are affected by interrupts.

As well as the above, the NSSC II is equipped with a set of short precision (16-bit) instructions which operate with 16-bit fixed point twos complement numbers. They are manipulated in the lower half of the general-purpose registers and there is no sign extension as on a S/360. A long precision fixed point (64-bit) instruction set is available also. An even-odd register pair is used for holding 64-bit numbers and only ADD, SUBTRACT, COMPARE, LOAD and STORE instructions are provided.

7

The ASPS executive has the primary goal of providing scheduling in real time of certain processes. There are three time periods of interest. At present they are 10 milliseconds, 100 milliseconds and 1 second but these may be adjusted. These time periods will be referred to here by the symbols T(1), T(2), and T(3), in millisecond time units. Associated with these time periods are three sets of processes. The set  $\{P(1,j)\}$  is associated with T(1), the set  $\{P(2,j)\}$  with T(2) and the set  $\{P(3,j)\}$  with T(3). Certain computations must be completed every T(1) milliseconds, others every T(2) milliseconds and still others every T(3) milliseconds. T(2) and T(3) are integer multiples of T(1), and T(3) is an integer multiple of T(2).

Timing is centered around an I/O interrupt from the DEA which is derived from, but not coincident with, the system master timing pulse. This interrupt will be generated by the DEA every T(1) milliseconds regardless of what the NSSC II does, although the NSSC II can mask it. On system start-up, the ASPS executive performs any data initializations which are necessary, signals the DEA that initialization is complete using direct I/O, and then places the NSSC II in the wait state with no processes active.

Processing begins when the first I/O inierrupt arrives from the DEA. From then on, P(1,j) must be completed every T(1), P(2,j) every T(2) and P(3,j) every T(3) millisecconds of real time for some j. Real time can be thought of as a sequence of T(3) time periods. Each T(3) time period is broken into an integral number of T(2) time periods, each T(2) time periods is broken into an integral number of T(1) time periods. The quantity j is called thee mode and a different process is used for each mode. The mode is the operating state of the platform and currently P(1,2) in P(2,3) is 4. They are called IDLE, COURSE, FINE and SLEW. The system changes mode based on certain inputs (see below) and only certain transitions are valid. Mode changes can only occur at the begining of a P(3,3) millisecond time period.

The NSSC II interval timer is <u>not</u> used for any determination of real time. It is used solely as a check on the system master timing pulse. At the beginning of each T(1) time period (i.e. following the interrupt from the DEA) the interval timer is loaded with a value slightly larger than T(1). If the timer ever expires then clearly an error has occurred. For the initial version of the executive, if the timer interrupt ever occurs, the system will not attempt to recover but merely inform the operator and enter the wait state.

When the I/O interrupt at the beginning of T(1) occurs the executive is entered. The DEA will already have completed a buffered input operation and placed a total of L(IN) words into the NSSC II memory. L(IN) is currently 38. This block of data is in two parts. The first

L(IN)-2 words are data for process P(1,j) and the last 2 are input to another process (see below). Prior to initiating P(1,j), these two words are removed by the executive and used to build a table in a separate memory area.

When P(1,j) completes, a table of outputs of length L(OUT) have been produced. L(OUT) is currently 32. A direct output is sent by the executive to the DEA which then begins a buffered output operation, i.e. the DEA removes the results of P(1,j) for its own use.

After the direct output has been sent, part of P(2,j) is run. For every j, the process P(2,j) must be completed in a T(2) time period. It is organized as a series, of subprocesses which, when executed in series constitute the entire process P(2,j). These subprocesses will be denoted P(2,j,k). For every j and k, the process P(1,j) and P(2,j,k) can be executed sequentially in less than P(1,j) milliseconds. Clearly k has to be less than or equal to P(2,j) in order to meet the deadline. The breaking of P(2,j) into a series of subprocesses is not a requirement but merely the process structure in the present design.

When P(2,j,k) completes, P(3,j) is resumed. It continues to execute until either:

- (a) the next I/O interrupt from the DEA occurs or

- (b) P(3,j) completes.

P(3,j) must be completed in a T(3) time period. P(3,j) for the current j is initiated at the beginning of each T(3) time period and following the completion of P(3,j) the processor will be in the wait state if P(1,j) or P(2,j) are not executing. P(3,j) operates on a table of data which is constructed for execution i of P(3,j) during execution i-1. The table is L(BACK) words long and is in fact constructed from from the 2 word blocks which were not input to P(l,j) during the executions of P(1,j) (see above). The first of these two words is a key and the second is a data word. If the key is negative, the data word is to be ignored. If the key is positive it consists of two parts. The first is an index indicating where in the data table the data word belongs. The second part is an identifier indicating to which of several possible tables the data word belongs. During any given T(3) time period all of the data words will be intended for the same data table. If the identifier changes during a given T(3) time period, an error has occurred.

Switching of modes can only occur between execution of P(3,j), i.e. at most only every T(3) milliseconds. One of the constituents of the data table for P(3,j) is a mode change indication. This designates the mode which the system will be in for the next T(3) time period. Valid mode

transitions have not yet been decided.

In addition to real time management, the executive must respond to the other sources of interrupt on the NSSC II. The machine check and program interrupts are both to be regarded as errors, and processing will consist of informing the operator and putting the system into the wait state. Supervisor call interrupts must provide supervisor services in the normal way and only two such services are presently defined. They are:

- (1) SVC code 55(hex) Process P(3,j) has ended.

- (2) SVC code AA(hex) Process P(1,j) has ended.

External interrupts are to be regarded as errors except for the interrupt generated by the operator from the TSE. Processing in this case is currently undefined and so all external interupt processing consists of informing the operator and putting the system into the wait state.

V. SUMMARY OF TIMING.

Refer to Fig. 3 for the system timing:

- (a) The PEA generates a sync pulse every T(1) milliseconds.

- (b) Starting at the trailing edge of the sync pulse, the DEA

- (c) The DEA interrupts the NSSC II when input is complete.

- (d) The NSSC II computes with the data and deposits the output in the buffer.

- (e) The NSSC II then signals the DEA to indicate that data is available.

- (f) The DEA begins to remove data from the output buffer in the  $\ensuremath{\mathsf{NSSC}}$  II.

- (g) The NSSC II then performs the next sequential parts of the T(2) msec computation.

- (h) Once (g) is complete the NSSC II reverts to background processing.

- (h) The sequence repeats.

FIGURE

FIGURE 2

Fast Loop Processing P(l,j)

-38-

Signal DEA That P(1,j) is complete

Data from NSSC II Buffer

Execution of P(3,j)